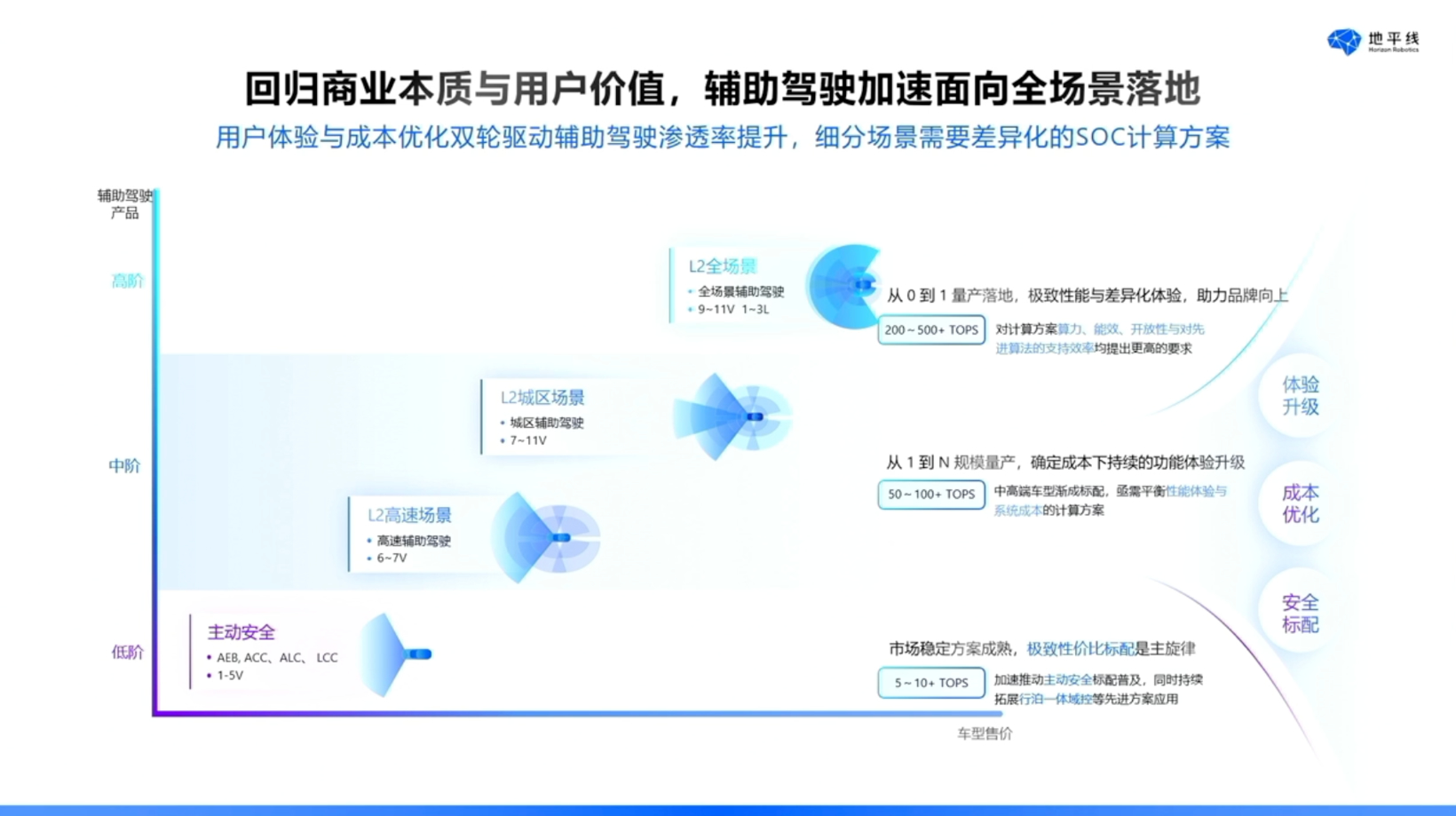

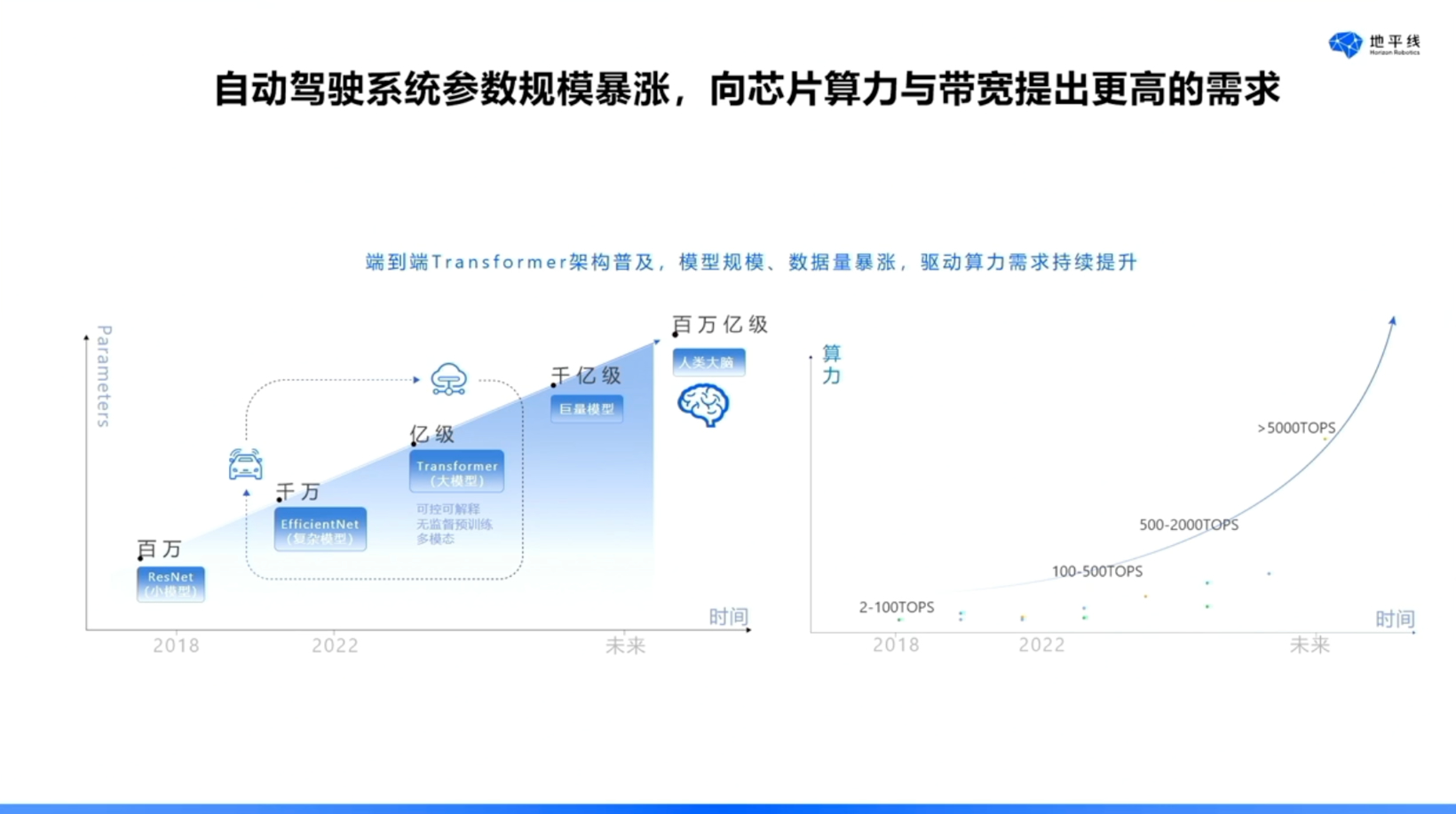

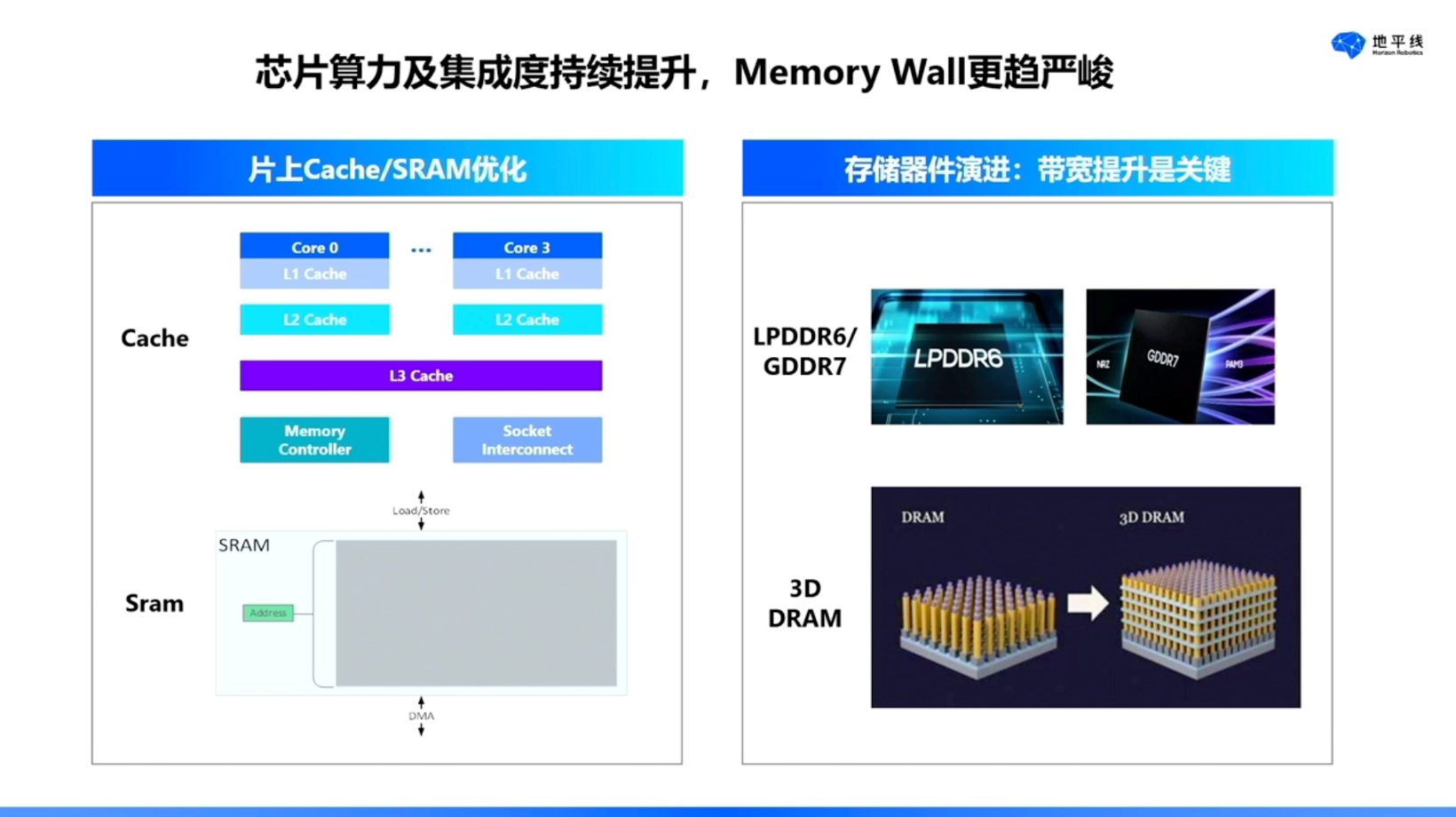

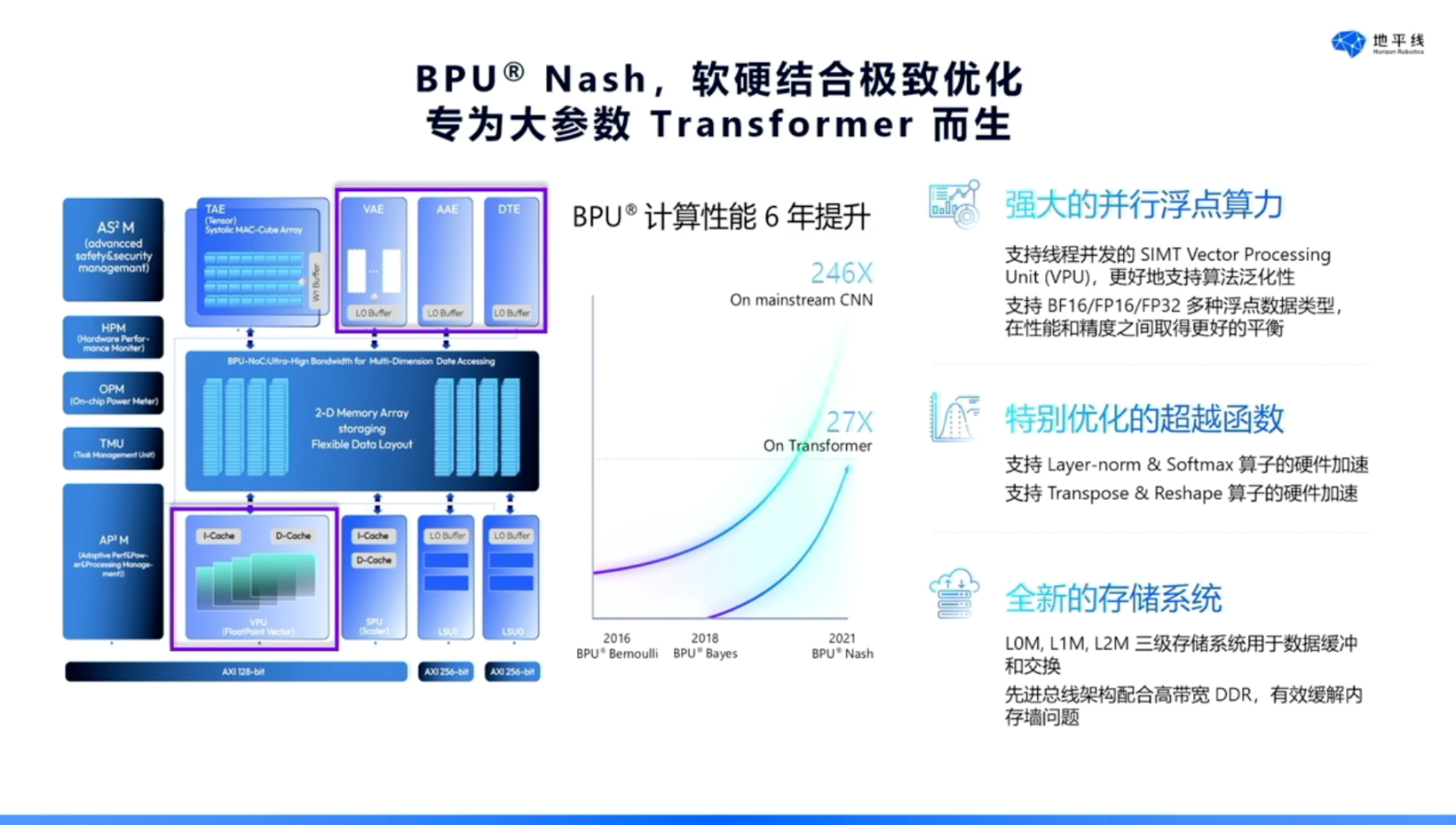

On July 22, 2025, at the 8th Intelligent Assisted Driving Conference, Shen Jian, Director of Chip Products at Horizon, pointed out that as the electronic and electrical architecture evolves towards central integration and computing, assisted driving algorithms and chips face higher demands. The application of end-to-end and large model technologies requires chips to possess high computing power, high bandwidth, and low latency. Shen introduced that Horizon is actively responding to these challenges by enhancing single-chip computing power, optimizing system efficiency, and reducing power consumption. He also stated that Horizon continues to innovate in chip architecture, having evolved through three generations to the Nash architecture, achieving significant improvements in CNN and Transformer processing performance and addressing the Memory Wall issue. Moreover, Horizon's Journey 6 series chips cover high, medium, and low-end markets comprehensively, with the J6P chip boasting a computing power of 560 TOPS set to enter mass production within the year. Horizon is a global leader in the field of all-scenario assisted driving. With a technology-oriented approach, the company currently has over 2,000 R&D personnel and more than 2,000 patents. Horizon has achieved remarkable results in international competitions and top academic conferences, gaining wide recognition for its contributions to assisted driving. By the first quarter of this year, the Journey series shipment volume has exceeded 8 million units, marking a significant achievement. In terms of market share, Horizon ranked second in the autonomous brand assisted driving solution market in 2023. By 2024, the company’s market share is expected to further increase, surpassing 33%, meaning that one in three vehicles equipped with assisted driving systems will utilize Horizon's solutions. Regarding the current industry development trends, the market can be divided into high, medium, and low-end segments. The low-end segment, which comprises entry-level products, has become a red ocean market, with core demands focusing on safety and cost-effectiveness. In the medium-end product sector, it is anticipated that the acceleration of assisted driving adoption over the past two years will lead to a qualitative change in shipment volumes and a rapid increase in penetration rates by 2025-2026. In the high-end product space, domestic companies and Tesla have been continuously exploring advanced assisted driving technologies. Thanks to efforts from major manufacturers in end-to-end and large model technologies, the industry has made significant progress in various scenarios and corner cases, greatly enhancing user experience. However, there remains a gap compared to human driving levels or ideal experiences, necessitating ongoing effort and exploration. Key points include prioritizing safety in all product tiers, maintaining high penetration rates for assisted driving, which will elevate cost demands for domain controllers and integrated machines, and expanding the user base, which will further raise user experience expectations. If user experience continues to improve, the adoption of assisted driving will increase, which is a common goal of the entire industry. The electronic and electrical architecture has evolved from distributed systems to regional control, and now towards central integration and computation, effectively reducing overall vehicle costs. Furthermore, various heterogeneous computing units are gradually transitioning to central computing SoCs to enhance assisted driving experiences. Regarding assisted driving algorithms and chips, discussions around 'end-to-end' and 'large models' are prevalent, involving technologies like VLM and VLA. These technologies significantly enhance assisted driving experiences but come with substantial costs due to their large model parameters, which can reach hundreds of millions. The current systems typically operate at frame rates of 10 to 20, which are expected to rise, necessitating higher chip performance. It is crucial that both end-to-end technologies and large models are based on Transformer architectures, which are sensitive to bandwidth and thus require higher chip bandwidth as parameters and frame rates increase. We believe the next generation of chips must possess high computing power, high bandwidth, and low latency as core features. To address these issues, we need to effectively break through single-chip computing power. The most direct way to enhance single-chip performance is through advanced process technology. This direction will continue, evolving from existing 7nm processes to 5nm, 4nm, and even 3nm. However, the performance gains from process upgrades are diminishing, necessitating system collaboration for effective breakthroughs in computing power. Improvements in computing power cannot rely solely on increasing accelerator capabilities; efficient data transmission to accelerators is critical to enhance overall system efficiency and achieve higher frame rates. This is the key to improving single-chip performance. The increase in computing power must meet practical automotive deployment needs, given that current automotive cooling systems typically maintain coolant temperatures around 65 degrees Celsius, imposing high energy efficiency requirements on chips. In assisted driving chips, NPUs consume the most power, making efficient NPU design crucial. Additionally, near-memory computing technologies and optimized physical implementations can further reduce power consumption, achieving effective computing power gains. The Memory Wall issue also becomes more severe with increased computing power and integration levels. Our considerations on this issue focus on two dimensions: on-chip SRAM and Cache. Enhancing computing power is supported by effective data transmission, while CPU Cache and NPU SRAM modules have high data transmission rates but limited capacity. External memory like DDR is needed to meet the large storage demands of current models, but DDR's speed significantly lags behind on-chip SRAM, making bandwidth enhancement for external storage a key task. The second dimension involves architecture. Common architectures in the market, such as Horizon's BPU and Huawei's Ascend series, exhibit excellent energy efficiency but are designed for specific domains, showing limitations in generalizability. To meet diverse scene requirements, DSA architectures are gradually integrating general acceleration units. For instance, GPU vendors have developed GPGPU combined with Tensor Core solutions for deep learning, which perform well in terms of generality but still fall short of DSA architecture in terms of energy efficiency and performance. Given the industry's shared goal of advancing higher-level assisted driving technologies, the integration of general computing architectures with dedicated computing architectures will become a trend. Horizon's existing BPU is based on DSA architecture but will evolve to incorporate general computing capabilities in the future. In the post-Moore era, relying solely on process advancements to enhance chip performance is becoming increasingly challenging. Industry trends indicate that manufacturers are now exploring performance potential through Design Technology Co-Optimization (DTCO) on advanced processes like A14 and A16. For assisted driving chips, similar strategies are needed, such as customizing standard cells at the chip level, achieving high-performance physical designs, and optimizing the collaboration between computing units and buses within the chip architecture to maximize performance. The system level can also draw from this approach by integrating more acceleration modules. At the algorithm level, promoting synergy between operators and chips and engaging in more customized code design will further enhance performance. Through multi-dimensional collaborative optimization, we can not only boost performance but also reduce energy consumption to some extent, thereby lowering thermal and power supply costs and achieving overall system optimization. Over the past decade, Horizon has conducted extensive practices in this field. In 2016, Horizon proposed the 'New Moore's Law for the Era of Intelligent Computing.' At that time, the industry widely believed that on-chip computing power equated to actual performance; however, today, clients prefer to verify chip performance through actual testing boards, reflecting that the performance of chips depends not only on their computing capabilities but also on compiler optimization, algorithm optimization, and other aspects. Therefore, only through collaborative optimization of hardware and software can we fully unleash chip performance. Since 2016, Horizon's chip architecture has evolved through three generations, from the original Bernoulli architecture to the subsequent Bayes architecture, culminating in the launch of the Nash architecture in 2021. The Journey 6 series chips currently in mass production are built on the Nash architecture. Regarding Nash architecture features, reflecting on the development of BPU over six years, it has achieved a 246-fold improvement in CNN processing performance and a 27-fold enhancement in Transformer processing performance. Additionally, this architecture has introduced a VPU to enhance chip generality. For commonly used specific transcendental functions within Transformers, we have implemented hardware-fixed designs to further boost overall Transformer performance. In terms of storage systems, the Nash architecture has introduced a new three-tier storage hierarchy, effectively addressing the Memory Wall issue through optimized collaboration between the cooperative bus and external DDR storage. With the recent completion of back-chip testing for the J6B chip, our Journey 6 series has achieved full compliance across high, medium, and low markets. Among them, the medium-end Journey 6E and Journey 6M chips entered mass production at the end of last year, while high-end and low-end products will also enter mass production soon. The Journey 6B has partnered with Bosch and is set for mass production in mid-2026. In the high-end product space, Horizon will continue to innovate and strive to provide clients with exceptional experiences. The Journey J6B chip focuses on solidifying foundational performance, making safety features a core standard, and strictly adhering to the principle of safety first. Additionally, the Journey J6P chip has a computing power of up to 560 TOPS, equipped with 18 A7 octa-core processors, an internal CNN bus bandwidth of 1Tb/s, image processing bandwidth performance of 5.3Gpixel/s, and built-in MCU to help clients reduce costs, with bandwidth exceeding 200G. The assisted driving solution powered by Journey 6P is set for its debut mass production in Q3 on the Chery Star Era E05.

Horizon Chip Product Director Discusses Advancements in Autonomous Driving Technology

Images

Share this post on: